Three Dimensional Integration

| |

|

| |

3D characterization |

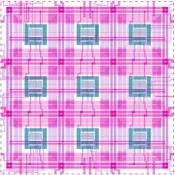

This research studies the impact of three dimensional integration on system efficiency beyond stacking heterogenous technologies and memory stacking. We designed a very simple 3D asynchronous FPGA architecture, as well as fabricated a chip to characterize thermal properties and variability in 3D integrated circuits.

- Collaborators

- Sandip Tiwari

- Students

- Benjamin Hill (Ph.D. 2015)

- Carlos Tadeo Ortega Otero (Ph.D. 2014)

- Jonathan Tse (Ph.D. 2015)

- Publications

- Jonathan Tse, Benjamin Hill, and Rajit Manohar.

A Bit of Analysis on Self-Timed Single-Bit On-Chip Links.

Proceedings of the 19th IEEE International Symposium on Asynchronous Circuits and Systems (ASYNC), May 2013.

(abstract, pdf)

- T. Robert Harris, Shivam Priyadarshi, Samson Melamed, Carlos Otero, Rajit Manohar, Steven R. Dooley, Nikhil M. Kriplani, W. Rhett Davis, Paul D. Franzon, and Michael B. Steer.

A Transient Electrothermal Analysis of Three-Dimensional Integrated Circuits.

IEEE Transactions on Components and Packaging Technologies, 2(4):660–667, April 2012.

(abstract)

- S. Priyadarshi, T. R. Harris, S. Melamed, C. Otero, N. Kriplani, C. E. Christoffersen, R. Manohar, S. R. Dooley, W. R. Davis, P. D. Franzon, and M. B. Steer.

Dynamic electrothermal simulation of three dimensional integrated circuits using standard cell macromodels.

IET Circuits, Devices, and Systems, 6(1):35–44, January 2012.

- Filipp Akopyan, Carlos Tadeo Ortega Otero, David Fang, Sandra Jackson, and Rajit Manohar.

Variability in 3-D Integrated Circuits.

Proceedings of the IEEE Custom Integrated Circuits Conference (CICC), September 2008.

(abstract, pdf)

- David Fang, Christopher LaFrieda, Song Peng, and Rajit Manohar.

A 3-Tier Asynchronous FPGA.

Proceedings of the 23rd International VLSI/ULSI Multilevel Interconnection Conference (VMIC), September 2006.

(abstract, pdf)

- Song Peng and Rajit Manohar.

Yield Enhancement of Asynchronous Logic Circuits through 3-Dimensional Integration Technology.

Proceedings of the ACM Great Lakes Symposium on VLSI (GLVLSI), April 2006.

(abstract, pdf)

- Christianto C. Liu, Jeng-Huei Chen, Rajit Manohar, and Sandip Tiwari.

Mapping Multimedia Applications to 3-D System-on-Chip.

Proceedings of the 2005 IEEE International Symposium on Circuits and Systems, May 2005.

|